# Optimized Cu-Contacted Si Nanowire Anodes for Li Ion Batteries Made in a Production Near Process

H. Föll, <sup>a,\*,z</sup> J. Carstensen, <sup>a</sup> E. Ossei-Wusu, <sup>a</sup> A. Cojocaru, <sup>a,\*</sup> E. Quiroga-González, <sup>a</sup> and G. Neumann <sup>b</sup>

<sup>a</sup>Institute for Materials Science, University of Kiel, Kaiserstr. 2, 24143 Kiel, Germany

Anodically etching macropores in Si substrates followed by chemical over-etching and Cu galvanics allows producing Si nanowire anodes for Li ion batteries with optimized geometry. This paper focuses on the optimizations of the process chain. The times for key processes could be substantially reduced while concomitantly improving the quality and the process window. The process chain now is close to enabling mass production on 200 mm wafers.

© 2011 The Electrochemical Society. [DOI: 10.1149/1.3561661] All rights reserved.

Manuscript submitted November 29, 2010; revised manuscript received February 8, 2011. Published March 28, 2011. This was Paper 440 presented at the Las Vegas, Nevada, Meeting of the Society, October 10–15, 2010.

The promise of affordable electrical cars in the near future can only be met if major progress will be made with respect to the Li ion battery performance. The energy per kg of present state-of-the-art Li ion batteries is at best around 2% of that of liquid fuel, and batteries with a substantially higher specific capacity are needed. The capacity of a Li ion battery is directly proportional to the amount of Li that can be intercalated into a weight unit of the anode (and cathode); it is typically expressed in mAh/g. Just as important for mass applications are specific costs expressed, e.g., in €/Wh.

In what follows only the anode of a Li ion battery will be considered. The maximum capacity of the present state-of-the-art graphite anodes is about of 370 mAh/g. In practice this number is somewhat lower and found in the 330 mAh/g range. <sup>1</sup>

It has been known for some time that Si would make a much better anode with a nominal anode capacity of 4200 mAh/g, more than ten-fold that of standard graphite anodes.<sup>2</sup> Just as important, most (>80%) of the Li can easily be taken out again, and a Si/Li anode just reduces the possible battery voltage by about 0.5 V upon discharging, thus not much more than the standard graphite anode. Despite these obvious advantages, bulk Si is useless as an anode, because the intercalation of Li leads to a volume expansion of up to a factor of 4, and the resulting stress will invariably fracture bulk Si into dust.

In a groundbreaking paper Chan et al. showed in 2008 that this problem could be overcome by using nano-structured Si in the form of nanowires. Si nanowires, while doubling their diameters during the intercalation of Li, do not fracture if they are thin enough. Some random arrangements of nanowires, with a diameter distribution centered around 90 nm were tested in Ref. 1; it was found that they could withstand more than ten charging/discharging cycles without significant loss of capacity. Meanwhile, substantial progress has been made concerning nano-structured Si as anode material <sup>1,3,6–8</sup> and the viability of the approach is now beyond reasonable doubt. While large-scale tests in batteries are not yet available, all results obtained so far indicate that nano-structured Si might meet all battery requirements and thus might be found in commercial batteries of the near future.

The nanowires in most papers addressing this topic were grown with the standard vapor-liquid-solid (VLS) technique, using mostly "Au droplets" as catalytic growth sites, <sup>1,7,9,10</sup> or by metal-assisted catalytic etching of single-crystalline silicon. <sup>5,11</sup> This paper addresses an alternative way for producing suitable Si nanowire anodes. First the basic techniques for producing Si nanowire arrays with optimized geometry via macropore etching in Si and Cu galvanics will be briefly described. Next, relevant test results with these anodes tried in standard batteries will be presented. The main part of the paper then deals with the substantial improvement of the structure of the anodes concerning to the drawbacks observed in the

previous results; the concomitant reduction of process costs by optimizing the process chain is also discussed.

#### **Basic Process for Producing Nanowire Anodes**

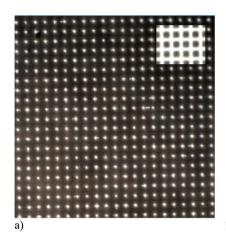

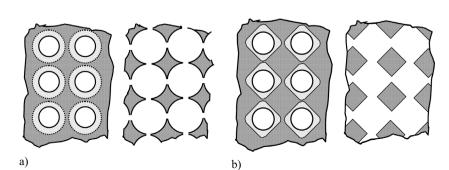

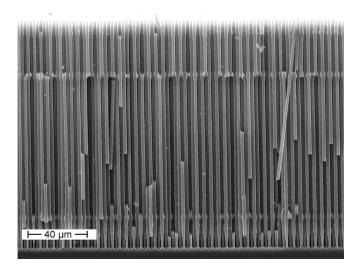

Macropore etching and subsequent nanowire array production.— The basic procedure for making nanowire arrays consists of two processes: (i) anodically etching macropores into p-type (or n-type) Si wafers, and (ii) chemically over-etching the pores (i.e., increasing their diameters) until pore walls touch and only the interstices = nanowires are left, see Fig. 1a.

The first step is to produce arrays of nuclei for the subsequent macropore etching process by (cheap) standard contact lithography. The lattice type and lattice constant a of the array determines the distance between the nanowires and the "Si efficiency" SE, i.e. the ratio of the Si volume remaining in the nanowires to the Si volume removed. Knowing from experiments that the volume expansion of the Si nanowires is practically completely due to a change of their lateral dimensions (i.e. doubling of their diameter), the best possible Si efficiency value is SE = 0.25 since at least  $^{3}/_{4}$  of the Si needs to be removed to allow for expansion in the lateral direction.

Etching Si macropores in arrays with lattice constants between about 0.5 and 10  $\mu m$  is fairly routine by now, cf. Refs. 12 and 13 It can be done either in lightly doped n-type or p-type Si. For what follows, typically 1 cm² sized p-doped {100} Si with doping levels corresponding to a resistivity of 15–24  $\Omega$  cm was used. The electrolyte was typically HF 5 wt % diluted with DMF. Typical etching conditions were: temperature  $T=20^{\circ}\mathrm{C}$ ; current density j=3-23 mA/cm², following some optimized function of time; total etching time around 110 min for pore depths around 150  $\mu$ m. Etching equipment from ET&TE (Ref. 14) was used, details of the process are described elsewhere. The etching process was monitored and controlled in-situ by impedance spectroscopy, cf. Ref. 15.

Increasing the pore diameters by isotropic chemical over-etching using well-documented HF/HNO<sub>3</sub>/HAc mixtures<sup>16,17</sup> is simple in principle but time consuming and difficult in reality (small process window). It can be done, however; more details are given in Sec. 4.

Isolating the substrate by a galvanically deposited Cu layer.—The nanowire structure shown in Fig. 1 cannot yet be used as a good anode because the Si substrate at the bottom of the nanowires will also incorporate some Li. Subsequent fracture destroys the structure within a few charge/discharge cycles. This can be avoided by depositing a several  $\mu m$  thick Cu layer (which is impervious to Li) on top of the substrate, effectively embedding the nanowires in an unyielding Cu layer that also thus provides the best possible electrical contact or current collector.

However, as found out in recent years, <sup>18–22</sup> Cu galvanics, while routinely used in metallurgy and Si microelectronics, is far from easy inside macropores and not yet well understood. This is also true for depositing Cu at the bottom of a nanowire array. While it

<sup>&</sup>lt;sup>b</sup>Fraunhofer Institute for Silicon Technology ISIT, Fraunhoferstr. 1, 25524 Itzehoe, Germany

<sup>\*</sup> Electrochemical Society Active Member.

z E-mail: hf@tf.uni-kiel.de

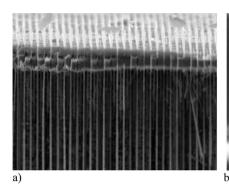

Figure 1. (Color online) (a) Top view of nanowire array; the lattice constant is 4  $\mu$ m. The inset shows the macropores before over-etching. (b) Cross-section of ordered nanowire array: (b) Shows a cross-section of a nanowire array produced in this way. It also demonstrates two pertinent points: (i) the nanowires are very stable and not given to fracture when mechanically challenged; (ii) there is a tendency for "stiction," i.e., a bunch of nanowires stick together like wet hair upon removal from the liquid. In contrast to wet hair, however, they do not come apart again when dried.

could be expected that the nanowires will not be coated with Cu since they are rather bad conductors, it nevertheless proved to be difficult to produce a homogenous Cu layer on top of the remaining Si substrate. The key to success was rather slow processing with optimized electrolytes and deposition conditions. Basic Cu deposition data were as follows: Electrolyte composition: 300 ml  $\rm H_2O$ , 70 ml  $\rm H_2SO_4$ , 5 g CuSO\_4, 0.1 g DTAC (1-dodecyl-trimethylammoniumchloride, 97%), 0.1 g SPS (Bis-3-sodiumsulfopropyl-disulfide), 0.1 g PEG (Polyethylenglycol). The Cu deposition was done at constant 20°C under potentiostatic conditions with a constant applied potential of -0.5 V for times around 10 h.

The long processing times in this case are problematic from cost considerations; in Sec. 4 it will be shown how this problem can be circumvented.

#### Major Test Results of the Nanowire Anode

The half-cell used for first tests has a Li reference electrode instead of a standard cathode; the separator is a glass fiber fleece. The standard LP-30 (Merck) electrolyte (0.5 ml) consists essentially of dimethylcarbonate and ethylencarbonate (1:1) plus 1 mol/l of LiPF<sub>6</sub>. The system is mounted under Ar atmosphere into a cylindrical Ti housing and pressed together mechanically.

Test batteries are similar to the half-cell, but use a standard NCM (LiNi $_x$ Co $_y$ Mn $_z$ O $_2$ ) cathode and are laminated into an airtight Al-foils stack. Both half-cell and battery were assembled and tested under standard conditions in the Li ion battery R&D facility of the ISIT/Germany.  $^{23}$

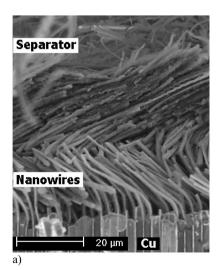

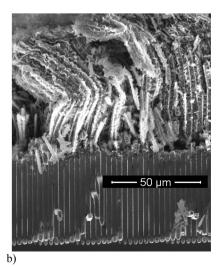

In what follows only some basic results are given without much details. Figure 2 shows SEM pictures of Si nanowire anodes after 6 and 66 cycles, respectively. The (beneficial) formation of SEI and the mechanical stability is clearly visible.

These anodes were used in the half-cell described above. Charging and discharging follows standard ISIT procedures, e.g. charging with C/10 (with C= nominal capacity and 10 h being the charging time) for the first eight cycles, for the remaining cycles C/5 was used as charge/discharge rate.

Figure 2 also shows the Cu layer and the separator material (needed to avoid accidental short circuits between anode and cathode). The nanowire array bends, as could be expected under the circumstances, but no breakage appears to take place during battery operation. Figure 2b, in particular, shows the presence of the necessary SEI (the wavy-looking structure) that eventually will embed and thus stabilize all nanowires.

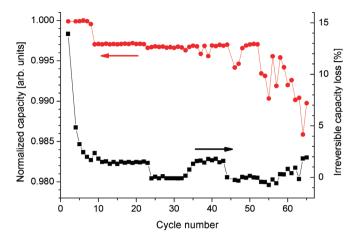

A satisfying performance was found with most but not all samples. Figure 3 shows the overall performance of a good anode used in an otherwise standard battery design for 66 cycles. The full capacity of Si was realized, the irreversible Li losses are around 14% in the first cycle and thus acceptable, and no detectable loss of capacity was observed.

Not all anodes showed top performance, however. The reason for this was found to be occasional Li leakage into the substrate because the Cu layer was not always absolutely impermeable to Li. In particular, the edges of the sample may "leak", and pinholes in the Cu layer on occasion also provided for local Li leakage to the Si substrate. Li incorporation into the Si substrate generally

**Figure 2.** SEM cross-section of Si nanowire anode after 6 cycles (a) and 66 cycles (b) in a half-cell. Note that nanowire breakage occurred during specimen preparation by cleaving and not during operation.

**Figure 3.** (Color online) Normalized charge capacity (normalized to its maximum capacity, around 4200 mAh/gr) of the Si nanowire anode, and its irreversible capacity loss. Appreciable irreversible losses of up to 13.9% are present mainly during the first 8 cycles, and then the loss is close to zero. The observed negative values of loss in some cycles are due to small leakage currents.

compromises the anode quality during cycling and thus must be prevented. In the following section it will be shown how this effect can be completely eliminated.

# **Process Improvements**

While the process chain described so far demonstrated the general validity of the approach, the process needed to be improved to allow cost efficient mass production of high quality anodes. The authors of this report have accomplished the improvement of the structure of the anodes in several ways, what could be translated into a better performance of the anodes and a reduction of costs. The optimization steps are addressed in the following lines:

- 1. Optimizing macropore etching.

- 2. Optimizing the nanowire geometry and the Si efficiency SE.

- 3. Minimizing the processing time for the chemical over-etch and enlarging the process window.

- 4. Avoiding stiction of the nanowires.

- 5. Minimizing the processing time for Cu galvanics.

- 6. Avoiding Li ion leakage to substrate silicon.

- 7. Optimizing the use of expensive Si wafers.

Progress to point 1 requires "fast" pore etching in large Si wafers (200 mm) under tight process control. All these points have been dealt with in prior work of our group and the reader is referred to 12, 24 and 25).

Substantial progress to the points 2–7 is achieved by etching macropores with diameters that are not constant but vary with depth in a specially tailored way. Again, the necessary hard- and software for etching macropores with variable diameters into 200 mm Si substrates has been developed before in our group, <sup>12,25</sup> and the process is already as fast and cost-efficient as can be.

Point 2 and to some extent point 3 is met by using a KOH (or TMAH) based anisotropic etch under condition where the {110} planes are stop planes for etching ( $C_{\rm KOH} = 0.45$  wt %,  $T = 50^{\circ}$ C, etching time = 90 min). This principally allows for an optimal SE value of up to 0.25. In comparison, pores in a square array with circular cross-sections and isotropic over-etching lead at best to SE(square) = 0.21 (see Fig. 4a); an hexagonal close-packed array would have SE(hex) = 0.1. Maximum Si usage is thus achieved with the new technique.

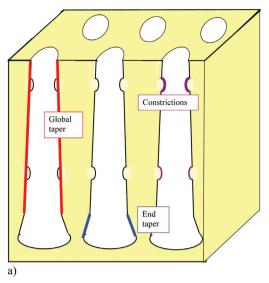

The anisotropic etching already reduces the processing time for the chemical over-etch (point 3) substantially. Tapering the pores globally as shown in Fig. 5 provides for further progress. The effect of the global taper is that less Si needs to be dissolved deep in the pores, allowing for a gradient in the dissolution rate as a function of depth. This balances to some extent the slower dissolution rates deep down in the pores because of diffusion limitation. The total effect of the measures taken with respect to points 2 and 3 is an optimal SE factor, a reduction of the processing time from  $\sim$ 15 h for the isotropic etch to 1.5 h for the anisotropic etch with global taper. A far larger process window is realized, too, since the anisotropic etch does not have autocatalytic components like the isotropic etch that make the process non-linear and hard to control.

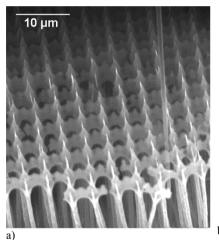

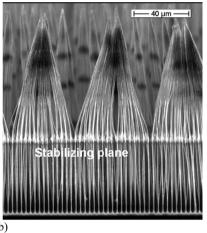

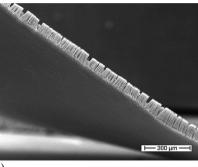

Point 4, the avoidance of stiction, is addressed by introducing pore diameter constrictions, as shown in Fig. 5. Two or more constrictions are introduced at suitable depths of the pores. This requires some complex control of the etching parameters since any constriction will change the subsequent etching behavior during continued pore growth. The effect of the constrictions is clear. Since at the places of the constrictions more Si needs to be dissolved before pore walls touch, limiting the dissolution time will assure that this does not happen at the depth of the constrictions. The result is that a stabilizing Si layer is present between the nanowires that prevents them from touching by stiction. Figure 6 provides a picture of this. One stabilizing layer might not be sufficient to avoid stiction as shown in Fig. 6b, but two or more layers are sufficient, cf. Fig. 7.

The decisive advantage of stabilizing the nanowires against stiction is that the surface is still well defined. This allows addressing points 5–7 in one fell swoop. Copper can now be deposited on the top of the nanowire structure and the resulting copper-nanowire "nanofur" may now be removed from the substrate. The latter step is facilitated by the end tapers shown in Fig. 5a, which ensure that the nanowires are very thin at the meeting point with the substrate as seen in Fig. 6a, showing a removed layer upside down. Figure 8a shows Cu on top of the nanowires and Fig. 8b a peeled off "nanofur". The "nanofur" is a finished anode; all that remains to be done is attaching it to a current collector.

**Figure 4.** Macropores in a square array (white circles) and the resulting nanowire structure after (a) isotropic over-etching (shaded circles) and (b) anisotropic over-etching.

**Figure 5.** (Color online) (a) Tailoring the macropore diameter. The global taper re-duces over-etching time, and the constrictions provide the stabilizing planes preventing stiction. (b) Pores with end taper.

**Figure 6.** (a) Looking at the bottom of a detached nanowire array with a clearly visible stabilizing layer. (b) Effect of one stabilizing plane on stiction effects.

Figure 7. Fully optimized nanowire structure with SE  $\approx$  0.5, two stabilizing layers preventing stiction and decreased diameters close to the substrate.

The Si substrate after detaching the "nanofur" can be reused; point 7 thus has been successfully addressed, too. Leakage problems (point 6) cannot occur anymore because there is no bulk Si left.

Cu deposition on top of the nanowire array is in principle far easier and faster than at the bottom but provides some challenges on its own. While Cu deposition by some sputter technique could easily produce a coherent Cu layer with a thickness of several  $\mu$ m, the process is neither fast nor cheap. In addition, Cu adherence to Si is a (known) problem that may necessitate some intermediate layers such as TiN. The approach we pursue at present with some success (see Fig. 6b) is therefore electroless plating a seed layer followed by standard Cu galvanics; a fast and cheap process sequence. Simply immersing the nanowire array while still connected to the Si substrate into suitable Cu bath will deposit Cu electroless only on the nanowire tips because of diffusion limitation into the depth of the nanowires. To facilitate Cu deposition even more, a stabilizing layer can be introduced close to the top of the nanowires, providing a closed surface and a very efficient diffusion barrier. As soon as the top of the nanowires is covered with Cu, the path for Cu deposition deeper down is closed. This was one of the major problems

**Figure 8.** (a) Cu layer on top of the nanowire array deposited galvanically after electroless formation of a Cu seed layer. (b) A partially peeled off "nanofur" leaving a reusable substrate behind.

encountered when depositing Cu deep down in pores of nanowire arrays but works to our advantage now.

## Conclusion and Outlook

The process chain introduced in this paper establishes a technology base that lends itself to cheap mass production of Si nanowire anodes for Li ion batteries. The complexity of processing a 200 mm wafer is roughly comparable to that of a solar cell and can thus be projected to be around a few Euro after mass production has been established. The capacity of a 200 mm "nanofur" anode with an active nanowire length of 150  $\mu$ m, an SE factor of 0.25, and a Si weight of 2.3 g will be around 10 Ah. Assuming conservatively an average voltage of 2.5 V, we have an energy density of 25 Wh, which seems to be sufficiently large to warrant further work.

It is clear that upscaling the process to a 200 mm technology requires substantial work, time and money. Nevertheless, we are confident that large-area Si nanowire anodes can be made and tested within the next year.

#### Acknowledgment

The intense and fruitful cooperation with the Fraunhofer Institute for Si Technology (ISIT) in Itzehoe/Germany on everything concerning batteries and battery testing is gratefully acknowledged.

University of Kiel assisted in meeting the publication costs of this article.

## References

- C. K. Chan, H. Peng, G. Liu, K. McIlwrath, X. F. Zhang, R. A. Huggins, and Y. Cui, Nat. Nanotechnol., 3, 31 (2008).

- 2. B. A. Boukamp, G. C. Lesh, and R. A. Huggins, J. Electrochem. Soc., 128, 725 (1981).

- H. Föll, H. Hartz, E. K. Ossei-Wusu, J. Carstensen, and O. Riemenschneider, *Phys. Status Solidi (RRL)*, 4, 4 (2010).

- R. Ruffo, S. S. Hong, C. K. Chan, R. A. Huggins, and Y. Cui, *J. Phys. Chem. C*, 113, 11390 (2009).

- 5. R. Huang, X. Fan, W. Shen, and J. Zhu, Appl. Phys. Lett., 95, 133119 (2009).

- K. Kang, H. S. Lee, D. W. Han, G. S. Kim, D. Lee, G. Lee, Y. M. Kang, and M. H. Jo, *Appl. Phys. Lett.*, 96, 053110 (2010).

- Y. Yang, M. T. McDowell, A. Jackson, J. J. Cha, S. S. Hong, and Y. Cui, *Nano Lett.*, 10, 1486 (2010).

- E. Ossei-Wusu, A. Cojocaru, H. Hartz, J. Carstensen, and H. Föll, *Phys. Status Solidi A*, (In press).

- T. Shimizu, T. Xie, J. Nishikawa, S. Shingubara, S. Senz, and U. Gösele, Adv. Mater., 19, 917 (2007).

- B. M. Kayes, M. A. Filler, M. C. Putnam, M. D. Kelzenberg, N. S. Lewis, and H. A. Atwater, Appl. Phys. Lett. 91, 103110 (2007)

- A. Atwater, *Appl. Phys. Lett.*, **91**, 103110 (2007).

M. L. Zhang, K. Q. Peng, X. Fan, J. S. Jie, R. Q. Zhang, S. T. Lee, and N. B. Wong, *J. Phys. Chem. C*, **112**, 4444 (2008).

- H. Föll, M. Christophersen, J. Carstensen, and G. Hasse, *Mater. Sci. Eng.*, R., 39, 93 (2002).

- 13. V. Kochergin and H. Föll, *Porous Semiconductors: Optical Properties and Applications*, Springer, London (2009).

- ET & TE Etch and Technology GmbH, http://www.et-te.com, last accessed Nov. 15, 2010.

- J. Carstensen, E. Foca, S. Keipert, H. Föll, M. Leisner, and A. Cojocaru, *Phys. Status Solidi A*, 205, 2485 (2008).

- J. E. A. M. van den Meerakker, R. J. G. Elfrink, W. M. Weeda, and F. Roozeboom, *Phys. Status Solidi A*, 197, 57 (2003).

- 17. X. G. Zhang, *Electrochemistry of Silicon and Its Oxide*, Kluwer Academic/Plenum Publishers, New York (2001).

- F. A. Harraz, K. Kamada, J. Sasano, S. Izuo, T. Sakka, and Y. H. Ogata, *Phys. Status Solidi A*, 202, 1683 (2005).

- C. Fang, E. Foca, L. Sirbu, J. Carstensen, I. M. Tiginyanu, and H. Föll, *Phys. Status Solidi A*, 204, 1388 (2007).

- C. Fang, E. Foca, S. Xu, J. Carstensen, and H. Föll, *J. Electrochem. Soc.*, **154**, D45 (2007).

- K. Fukami, Y. Tanaka, M. L. Chourou, T. Sakka, and Y. H. Ogata, *Electrochim. Acta*, 54, 2197 (2009).

- M.-D. Gerngroß, H. Föll, A. Cojocaru, and J. Carstensen, *ECS Trans.*, 19(3), 347 (2009).

- ISIT: Fraunhofer Institute for Silicon Technology, http://www.isit.fraunhofer.de/ Publikationen/, last accessed Nov. 15, 2010.

- M. Christophersen, J. Carstensen, A. Feuerhake, and H. Föll, Mater. Sci. Eng., B, 69–70, 194 (2000).

- J. Carstensen, M. Christophersen, S. Lölkes, E. Ossei-Wusu, J. Bahr, S. Langa, G. Popkirov, and H. Föll, *Phys. Status Solidi C*, 2, 3339 (2005).